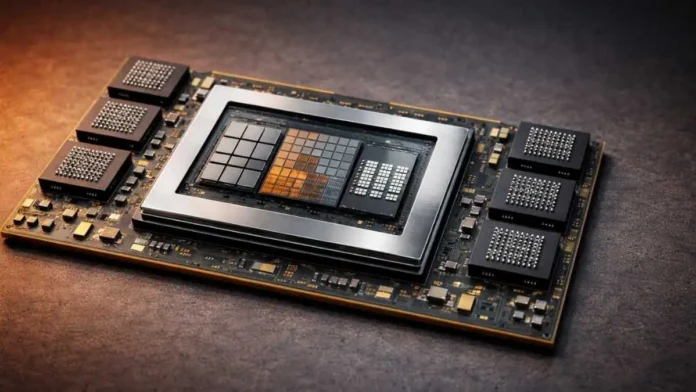

AMD’s upcoming Halo-class processor, expected to succeed the current Ryzen AI MAX lineup, may transition to LPDDR6 memory, according to recent industry chatter and roadmap leaks. If the information proves accurate, the move would represent one of the most substantial memory upgrades in the company’s mobile strategy and could significantly increase bandwidth for next-generation AI and gaming notebooks.

While AMD has not officially announced the successor platform, multiple hardware sources indicate that the future Halo design will align with the LPDDR6 standard, which is designed to reach speeds of up to 14,400 MT/s. Current Halo silicon uses LPDDR5X memory operating at up to 8,000 MT/s on a 256-bit interface, delivering 256 GB/s of theoretical bandwidth.

If the next-generation design maintains a 256-bit memory bus while adopting LPDDR6 at 14,400 MT/s, total bandwidth would approach 460 GB/s. That represents roughly an 80 percent increase over the original Halo configuration.

However, the shift to LPDDR6 introduces architectural nuances that extend beyond simple transfer-rate scaling. Unlike LPDDR5X, which uses 16-bit subchannels, LPDDR6 moves to a 24-bit subchannel structure. This change alters how memory controllers aggregate channels and could influence the effective bus topology of future Halo designs.

A configuration that is “256-bit” in LPDDR5X terms does not translate identically under LPDDR6’s signaling model. Depending on how AMD structures its controller, the company could theoretically move toward a 384-bit aggregate interface while maintaining similar package layouts, or retain a 256-bit equivalent configuration with higher per-channel throughput.

LPDDR6 is also expected to introduce refinements in signaling efficiency and optional metadata or ECC-style protection mechanisms integrated at the memory level. If portions of bandwidth are allocated for reliability features, effective usable throughput may differ slightly from peak theoretical figures. That distinction becomes increasingly relevant in AI-focused workloads, where sustained bandwidth consistency matters more than burst transfer rates.

The significance of an 80 percent bandwidth increase extends beyond synthetic benchmark improvements. Halo-class processors integrate large GPU blocks alongside CPU cores and dedicated AI accelerators within a unified memory architecture. In such systems, graphics workloads, neural inference tasks, and general CPU operations all share the same memory pool. As integrated GPU sizes grow and AI workloads expand, memory throughput increasingly becomes the primary constraint rather than raw compute capability.

This dynamic is particularly visible in local large language model inference. When model parameters exceed on-chip cache capacity, sustained memory bandwidth determines how quickly tokens can be processed.

In unified memory systems, higher throughput reduces contention between GPU compute kernels and CPU-side preprocessing threads. In practical terms, this can improve responsiveness for generative AI tools, real-time image synthesis, and hybrid rendering workloads without requiring discrete VRAM.

Reports also suggest the new platform could introduce Zen 6 CPU cores and RDNA 5 graphics architecture. Some roadmap discussions point to configurations reaching up to 24 CPU cores. If that scale materializes, higher memory bandwidth will be necessary to prevent performance bottlenecks, especially in mixed workloads involving rendering, AI inference, and multitasking. A 24-core CPU cluster sharing bandwidth with a substantially enlarged GPU tile would place far greater pressure on the memory subsystem than today’s Halo implementations.

Power and thermal considerations further complicate the transition. Driving LPDDR6 at 14,400 MT/s demands tighter signal integrity controls, improved board routing precision, and potentially higher power draw under sustained load.

In thin-and-light laptop designs, sustaining near-460 GB/s bandwidth without exceeding thermal envelopes will require careful tuning of voltage curves and memory controller efficiency. Wider effective bus implementations, if adopted, would also increase trace complexity and package-level design constraints.

This potential shift positions AMD against rival strategies in mobile silicon. Intel’s latest notebook platforms currently top out at LPDDR5X-9600 configurations, while Apple’s high-end SoCs rely on extremely wide unified memory interfaces to achieve elevated bandwidth ceilings. Rather than matching ultra-wide bus designs, AMD appears poised to leverage higher-frequency LPDDR6 signaling to narrow the gap while maintaining a modular chiplet-based approach.

Manufacturing timing remains an open question. LPDDR6 module density, yield maturity, and supplier ramp timelines will influence how quickly OEM partners can integrate the new standard into premium laptop platforms. Early LPDDR6 implementations may initially ship at lower densities or conservative speed bins before scaling toward the 14,400 MT/s ceiling. A projected launch window around 2027 to 2028 would provide memory suppliers sufficient runway to stabilize production and optimize cost structures.

Strategically, the next Halo generation may signal AMD’s deeper commitment to positioning its high-end APUs as full mobile workstation alternatives. With bandwidth approaching or potentially exceeding 460 GB/s, integrated graphics performance could narrow the gap with certain midrange discrete GPUs in bandwidth-sensitive scenarios, particularly at higher resolutions or in AI-accelerated creative pipelines.

It is also worth noting that bus-width decisions will ultimately determine how dramatic the uplift becomes. If AMD pairs LPDDR6 with an expanded aggregate interface rather than a direct carryover from LPDDR5X-era layouts, theoretical bandwidth could scale significantly beyond the initial 80 percent estimate. Conversely, if power or cost constraints limit interface expansion, gains may be more incremental but still meaningful within mobile envelopes.

Also Read: CXMT Starts Mass Production of LPDDR5X Memory Chips

It is important to note that AMD has not confirmed specifications, core counts, memory configurations, or launch timing. Roadmap details can evolve significantly before product release.

However, if LPDDR6 integration becomes a reality, it would represent more than a routine speed increase. It would underscore a broader shift in mobile computing, where memory bandwidth is emerging as one of the most decisive factors in AI and graphics performance. In that context, the next Halo processor could mark a meaningful turning point in AMD’s AI laptop strategy.

Source: Olrak29 (Twitter)